Contenuto

- Definizione: che cosa significa Staggered Pin Grid Array (SPGA)?

- Un'introduzione a Microsoft Azure e Microsoft Cloud | In questa guida imparerai cos'è il cloud computing e in che modo Microsoft Azure può aiutarti a migrare e gestire la tua azienda dal cloud.

- Techopedia spiega lo Staggered Pin Grid Array (SPGA)

Definizione: che cosa significa Staggered Pin Grid Array (SPGA)?

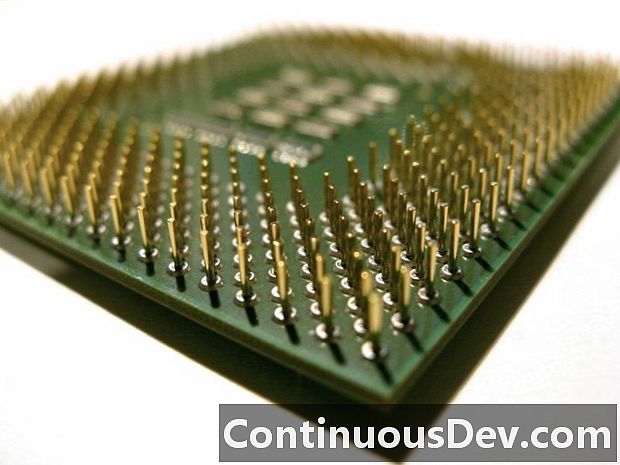

Un array di griglia di pin sfalsati (SPGA) è uno stile di presa di circuito integrato o pin-out avente una griglia di pin sfalsati che circonda il bordo delle prese, disposti come più quadrati, uno all'interno dell'altro. La struttura è anche conosciuta come quadrati intersecanti.SPGA viene generalmente utilizzato su schede madri per processori basati sulle piattaforme Socket 5, Socket 7 e Socket 8.

Un'introduzione a Microsoft Azure e Microsoft Cloud | In questa guida imparerai cos'è il cloud computing e in che modo Microsoft Azure può aiutarti a migrare e gestire la tua azienda dal cloud.

Techopedia spiega lo Staggered Pin Grid Array (SPGA)

In un array di griglie pin sfalsati (SPGA), i pin sono disposti in file diagonali. SPGA include due matrici quadrate di pin, bilanciate in entrambe le direzioni. In altre parole, i perni sono disposti in modo da formare un reticolo quadrato diagonale all'interno del confine quadrato. SPGA include un'area al centro del pacchetto in cui non sono disposti pin. I pacchetti SPGA sono ideali per quei dispositivi che richiedono una maggiore densità dei pin rispetto a ciò che un array di griglie pin standard (PGA) può offrire.I circuiti integrati iniziali avevano pin disposti utilizzando il PGA, che imposta i pin in una struttura a griglia. Il progresso nella progettazione del processore e la richiesta di più pin ha reso la PGA inappropriata e obsoleta. L'obiettivo principale di SPGA era ridurre le dimensioni del microprocessore quando sono necessari più pin. La struttura SPGA è utilizzata dai processori incentrati sulla tecnologia Socket 5, Socket 7 e Socket 8.

Il vantaggio di utilizzare una formazione SPGA rispetto alle versioni precedenti è che è costituito da pin più vicini, consentendo così più pin per una specifica area di superficie. Ciò consente di ridurre le dimensioni del microchip o, in altre parole, offre una migliore capacità di trasferimento in un chip di dimensioni simili.